en.radzio.dxp.pl

Main menu

Index

Privacy policy

Youtube channel

PCB Manufacturer

Tutorials

STM32F429I-DISCOVERY

STM32VLDISCOVERY

Code library for LCD

S1D15705

SSD1963

SED1335/RA8835

SED1520/NJU6450

SED1530/SPLC501C

KS0108/HD61202

S6B0724

T6963C

ATMEL AVR microcontrollers

HD44780 driver

1-wire driver

Delay utilities

Decoding RC5 infrared

iButton CRC computing

iButton reader

ATtiny2313 board

ATmega162 board

STMicro ST7 microcontrollers

Software I2C impementation

External I2C EEPROM memory

Projects

SPI bus sniffer

I2C bus sniffer

1-wire sniffer

AVR910 programmer

Software

Bitmap converter for LCD

Modbus Master Simulator

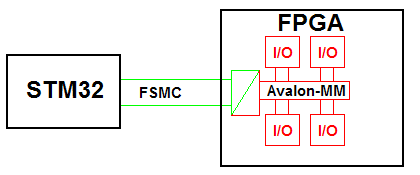

STM32 FSMC to Avalon bus wrapper

This wrapper converts STM32 FSMC interface signals (multiplexed) to Altera Avalon bus signals. It provide access to SOPC Builder/QSYS system peripherals from STM32 microcontroller.

Using this wrapper with QSYS SDRAM controller make easy way to use SDRAM memory with STM32 microcontroller (at this moment STM32 uC don't have SDRAM controller).

Source code (VHDL) of wrapper

--================================================================================================= signal address : std_logic_vector(31 downto 0); begin demux : process (CLK, RESET) AVALON_WRITEDATA <= data when HOST_NCS = '0' else (others => '0'); HOST_DATAOUT <= AVALON_READDATA(15 downto 0); HOST_NWAIT <= AVALON_WAITREQUEST when (((HOST_NWR xor HOST_NRD) = '1') and (HOST_NCS = '0')) else '0'; |