en.radzio.dxp.pl

Main menu

Index

Privacy policy

Youtube channel

PCB Manufacturer

Tutorials

STM32F429I-DISCOVERY

STM32VLDISCOVERY

Code library for LCD

S1D15705

SSD1963

SED1335/RA8835

SED1520/NJU6450

SED1530/SPLC501C

KS0108/HD61202

S6B0724

T6963C

ATMEL AVR microcontrollers

HD44780 driver

1-wire driver

Delay utilities

Decoding RC5 infrared

iButton CRC computing

iButton reader

ATtiny2313 board

ATmega162 board

STMicro ST7 microcontrollers

Software I2C impementation

External I2C EEPROM memory

Projects

SPI bus sniffer

I2C bus sniffer

1-wire sniffer

AVR910 programmer

Software

Bitmap converter for LCD

Modbus Master Simulator

What is I2C bus?

I2C is a serial two wire bus used in microcontrollers systems to

communication with devices such as EEPROM memories, digital

potentiometers, LCD controllers, RTCs and other. I2C bus uses only

two bidirectional open-drain lines : Serial Data (SDA) and Serial

Clock (SCL). This lines are pulled up with resistors (usually

4,7kOhms). For more details about I2C bus see : I2C on Wikipedia

Basics of I2C bus

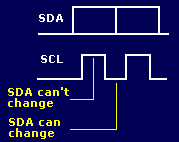

Generally, SDA state can change only if SCL is low. When SCL is

high SDA state can NOT change, except START and STOP signals. See

below picture:

START signal

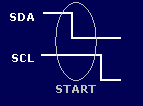

Start signal begins all transmission via I2C bus. Start

condition occurs when SDA line goes low (falling edge) when SCL line

is high. See below picture:

| Source code of i2c_start routine |

| ;----------------------------------------------------------------- ; START routine ;----------------------------------------------------------------- .i2c_start BRES I2C_DIR, #SDA ; set SDA BRES I2C_DIR, #SCL ; set SCL BSET I2C_DIR, #SDA ; falling edge on SDA CALL i2c_delay ; wait some microseconds BSET I2C_DIR, #SCL ; reset SCL RET |

STOP signal

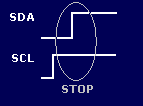

Stop signal ends all transmission via I2C bus. Stop condition

occurs when SDA line goes high (rising edge) when SCL line is high.

See below picture:

| Source code of i2c_stop routine |

| ;----------------------------------------------------------------- ; STOP routine ;----------------------------------------------------------------- .i2c_stop BRES I2C_DIR, #SCL ; set SCL CALL i2c_delay ; wait some microseconds BRES I2C_DIR, #SDA ; rising edge on SDA RET |

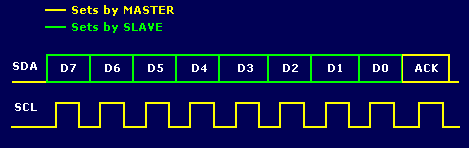

Master sends byte to slave device

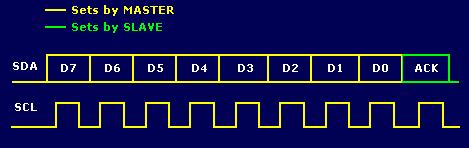

Master generate SCL signal, write eight data bits, from MSB to

LSB and read an ACK from Slave device.

Source code of i2c_write routine |

;----------------------------------------------------------------- |

Master receives byte from slave device

Master generate SCL signal, read eight data bits from slave

device and send ACK bit to slave device.

Source code of i2c_read routine |

;---------------------------------------------------------------- |

Download

Source file for ST7FLITE19 MCU :

File i2c.asm