en.radzio.dxp.pl

Main menu

Index

Privacy policy

Youtube channel

PCB Manufacturer

Tutorials

STM32F429I-DISCOVERY

STM32VLDISCOVERY

Code library for LCD

S1D15705

SSD1963

SED1335/RA8835

SED1520/NJU6450

SED1530/SPLC501C

KS0108/HD61202

S6B0724

T6963C

ATMEL AVR microcontrollers

HD44780 driver

1-wire driver

Delay utilities

Decoding RC5 infrared

iButton CRC computing

iButton reader

ATtiny2313 board

ATmega162 board

STMicro ST7 microcontrollers

Software I2C impementation

External I2C EEPROM memory

Projects

SPI bus sniffer

I2C bus sniffer

1-wire sniffer

AVR910 programmer

Software

Bitmap converter for LCD

Modbus Master Simulator

Lesson 6. Pulse Width Modulation (PWM)

In lesson 5 we learn how to blink led with Compare unit of timer TIM3. Compare unit can be also used in pulse width modulation mode for brightness control of LED. Now, go to section number 13.3.9 of RM0041 document.

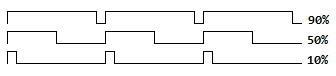

Different PWM duty

Configuration of compare module are slighty different from previous example :

TIM3->CCMR2 = TIM_CCMR2_OC4M_2 | TIM_CCMR2_OC4M_1 | |

Now, CCR3 and CCR4 registers holds PWM duty value. Write initial duty value to registers :

TIM3->CCR3 = 0; // Start PWM duty for channel 3 |

Each time when timer reload new value we want to change current PWM duty in both channels. So in interrupt handler from TIM3 we well be change duty on both channels. On CH3 we increase duty by 1% each time, on CH4 we decrease duty by 1% each time :

void TIM3_IRQHandler(void) |

Complete source code :

//============================================================================= #define LED_GREEN_GPIO GPIOC #if (LED_BLUE_PIN > 7) #if (LED_GREEN_PIN > 7) AFIO->MAPR = AFIO_MAPR_TIM3_REMAP; // Full TIM3 remap TIM3->PSC = 239; // Set prescaler to 24 000 (PSC + 1) TIM3->CCR3 = 0; // Start PWM duty for channel 3 TIM3->CCMR2 = TIM_CCMR2_OC4M_2 | TIM_CCMR2_OC4M_1 | TIM3->CCER = TIM_CCER_CC4E | TIM_CCER_CC3E; // Enable compare on channel 3 & 4 TIM3->DIER = TIM_DIER_UIE; // Enable update interrupt (timer level) while (1) {} |